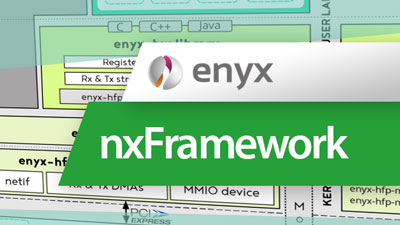

nxFramework FPGA Development Framework from Enyx

Build ultra-low latency apps for fintech using Enyx off-the-shelf solutions and the nxFramework.

The TCP/IP (Transmission Control Protocol/ Internet Protocol) is an Ethernet IP core for FPGAs that incorporates both the transport and internet layer protocols to deliver reliable, end-to-end network communications on the internet or private networks.

Chevin Technology’s TCP/IP Offload Engine is an FPGA Synthesizable Ethernet TCP/IP server/client in a lean and fast, all-RTL solution. The TCP IP core can be used with both 10G and 25G Ethernet IP cores for reliable, high performance connectivity in any FPGA using a minimum of resources. Chevin Technology’s TCP/ IP core offloads the TCP protocol using fast and efficient logic for checksum calculation, and is easily integrated alongside other protocols to provide an easy path for the development of TCP-enabled FPGA applications.

The IP core targets BittWare FPGA cards with AMD Virtex UltraScale+ and Altera Agilex 7 devices. Specific supported cards are listed under specifications.

The TCP/IP Offoad Engine provides a quick path to creating TCP enabled applications with a minimum of additional resources for network management at the FPGA side. The AXI4-Lite host interface permits control and configuration of the TCP IP core’s registers and statistics for connection and link monitoring. The User application side and MAC connect to the TCP IP core with an easy to use AXI4-Stream or Avalon interface.

The TCP IP core can be configured to initiate (client) or accept (server) a TCP connection with a remote endpoint. Once a session is established, data can be reliably sent and received over the TCP protocol; taking care of checksum insertion/checking, sockets and flow control at high, sustained data rates of 10 or 25 Gbit/s. The user interface provides flow control, and manages multiple connections.

Multiple simultaneous connections are supported, limited only by available packet buffer resources. Opening and closing connections is handled by the TCP core, with no requirement for additional software support. Re-transmit is handled by a control layer within the TCP for fast, easy error recovery. Statistics are collected for all sent and received frames for traffic and connection analysis.

TX / RX– Latency < 1 us

| Sessions | Resource | Usage |

|---|---|---|

| Altera Agilex F-Series | 32 | IA-840F card with all features enabled including memory mapped interface: 40k ALMs, 220 M20K |

| AMD Virtex UltraScale, Zynq | 16 | Small memory footprint: 110 BRAMs + packet buffer; 35000 LUTs |

Ethernet software vendor providing high performance, reliable data transfer capabilities for high end FPGAs.

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

Build ultra-low latency apps for fintech using Enyx off-the-shelf solutions and the nxFramework.

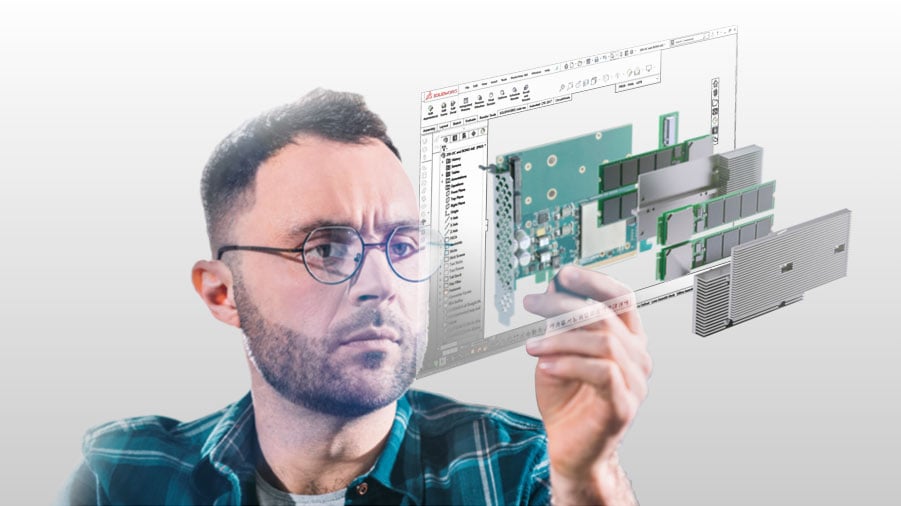

We examine our reference design for sustained 100 Gb/s capture to host DDR4 over a PCIe bus. Read the white paper, then request the App Note for even more detail!

Article Two Approaches to Rapidly Developing Customized FPGA Solutions How BittWare reduces risk over the complete customized solution lifecycle Overview While FPGAs in the datacenter

High-speed networking can make timestamping a challenge. Learn about possible solutions including card timing kits and the Atomic Rules IP TimeServo.

Notifications