UDP Offload Engine IP Core from Atomic Rules

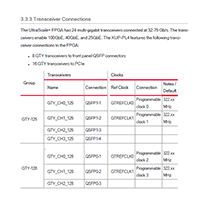

Go Back to IP & Solutions UDP Offload Engine UOE IP Core for 10/25/50/100GbE Atomic Rules UDP Offload Engine (UOE) is a UDP FPGA IP

Legacy Product Notice:

This is a legacy product and is not recommended for new designs. It is still available for purchase, but development tools and software are no longer maintained for compatibility with the latest FPGA tools and operating systems. Minimum order quantities (MOQs) may apply. Contact BittWare for details.

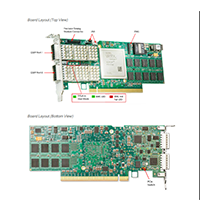

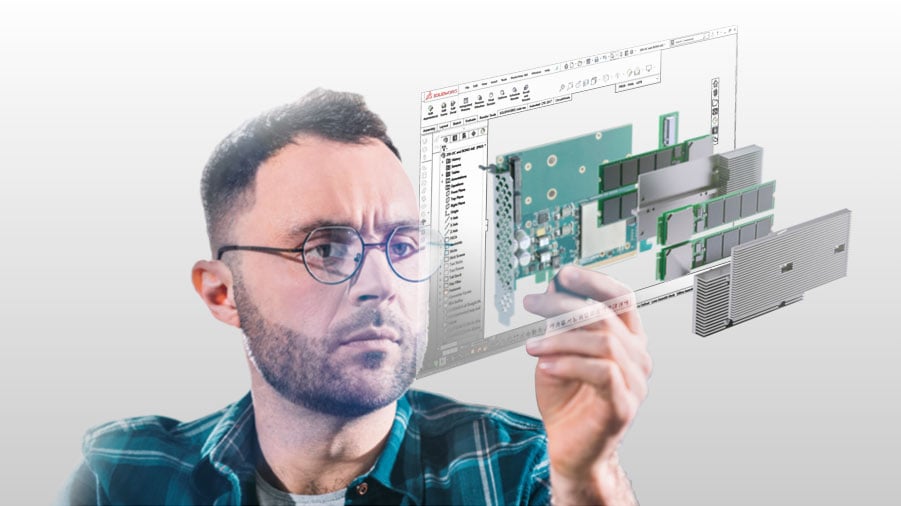

BittWare’s XUP-PL4 is a low-profile PCIe x16 card based on the AMD Virtex UltraScale+ FPGA. The UltraScale+ devices deliver high-performance, high-bandwidth, and reduced latency for systems demanding massive data flow and packet processing. The board offers up to 32 GBytes of memory, sophisticated clocking and timing options, and two front panel QSFP cages, each supporting up to 100 Gbps (4×25) – including 100GbE.

The XUP-PL4 also incorporates a Board Management Controller (BMC) for advanced system monitoring, which greatly simplifies platform integration and management. All of these features combine to make the XUP-PL4 ideal for a wide range of data center applications, including network processing and security, acceleration, storage, broadcast, and SigInt.

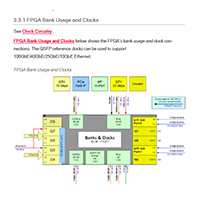

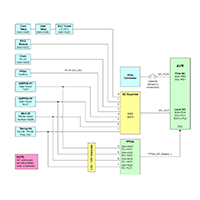

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

Get extended warranty support and save time with a pre-integrated solution!

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

Go Back to IP & Solutions UDP Offload Engine UOE IP Core for 10/25/50/100GbE Atomic Rules UDP Offload Engine (UOE) is a UDP FPGA IP

BittWare On-Demand Webinar Computational Storage Using Intel® Agilex™ FPGAs: Bringing Acceleration Closer to Data Watch Now on Demand! Accelerating NVMe storage means moving computation, such

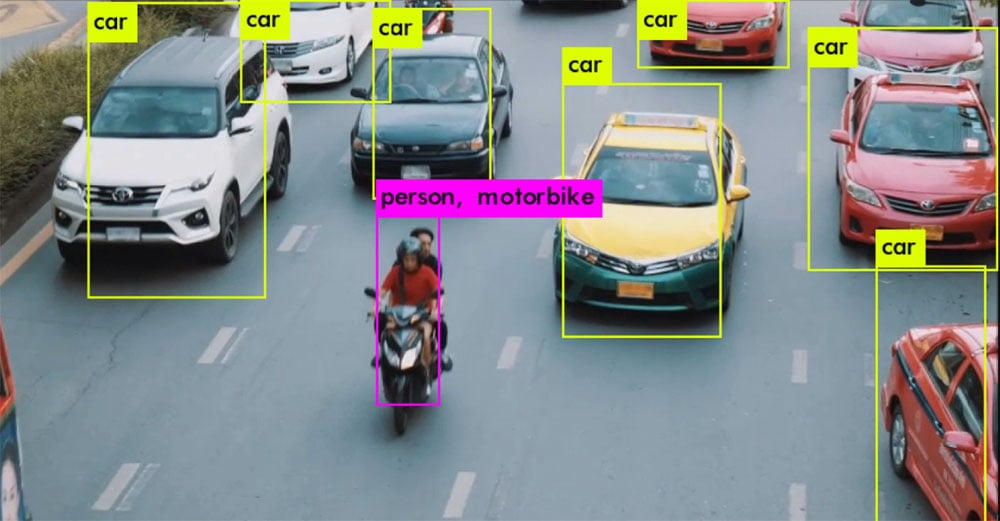

White Paper FPGA Acceleration of Binary Weighted Neural Network Inference One of the features of YOLOv3 is multiple-object recognition in a single image. We used

Article Two Approaches to Rapidly Developing Customized FPGA Solutions How BittWare reduces risk over the complete customized solution lifecycle Overview While FPGAs in the datacenter